Due to the IR drop chip temperature increases and it affects reliability the most. To participate you need to register.

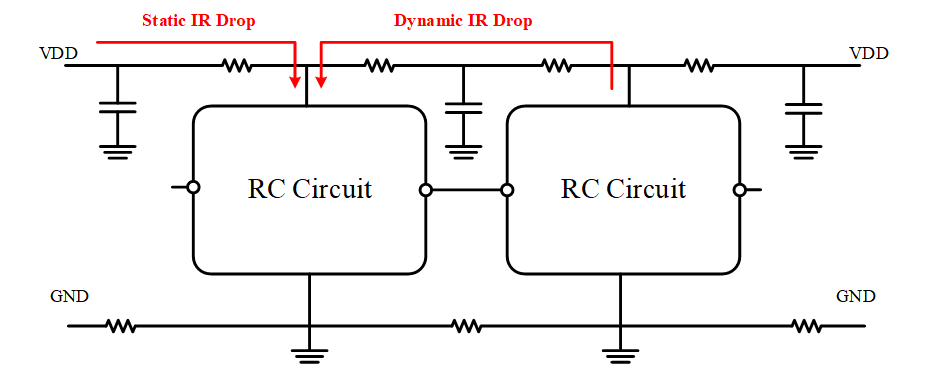

Compact physical IR-drop models of on-chip powerground distribution networks are derived for two generic types of packages.

. Package cross-section showing IR drop components Combining 3 4 and the value for IR chip found in 2 provides a formula for determining an actionable IR drop target for the physical design process. At the same time the IR drop is increased due to higher interconnect resistance. Chip dimensions metal coverage and piecewise distribution of the IC consumption are taken into account to obtain closed form expressions.

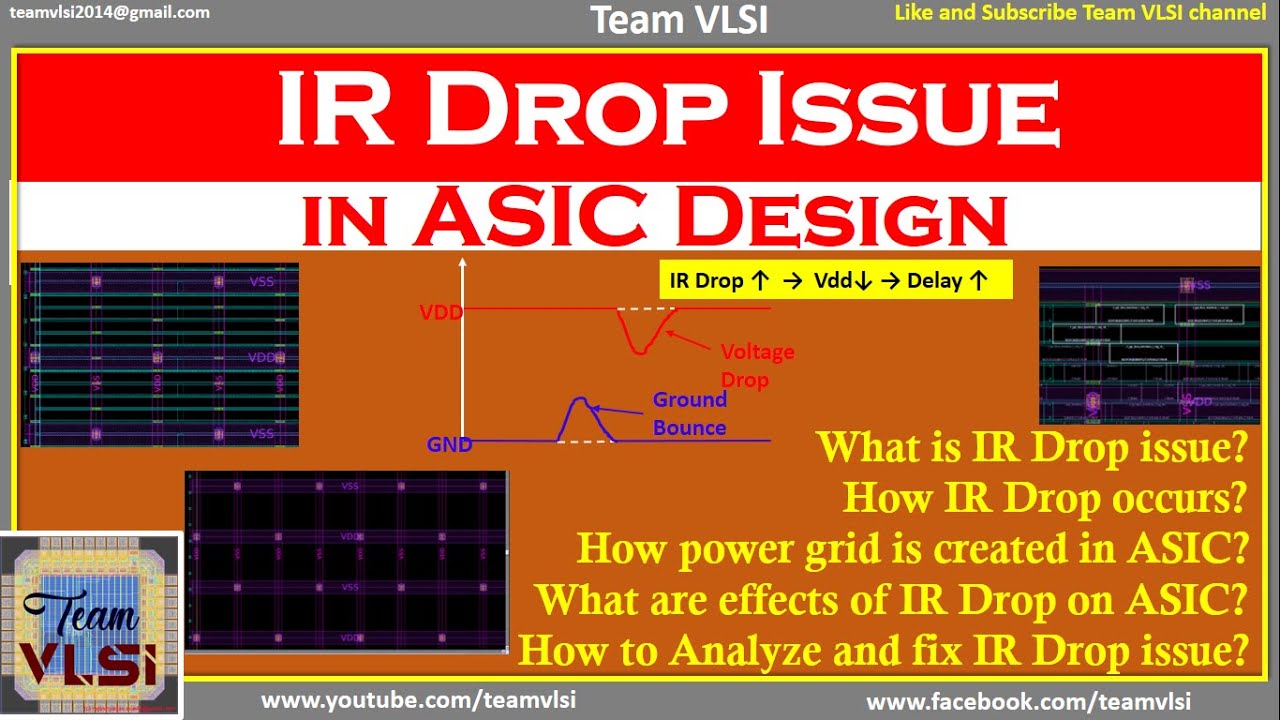

The power supply VDD and VSS in a chip is uniformly distributed through the metal rails. This Drop is called as IR Drop. For example a design needs to operate at 2 volts and has a tolerance of 04 volts on either side we need to ensure that the voltage across its power pin Vdd and ground pin Vss in that design does not fall short of 16 VoltsThe acceptable IR drop in this context is 04 volts.

Industry standard Project Execution 1. As a result there are very low noise and variation margins. IR Drop and EM Analysis IR Drop Drop happens in supply voltage when traverses through the power network.

Power planning means to provide power to the every macros standard cells and all other cells are present in the design. For example a design needs to operate at 2 volts and has a tolerance of 04 volts on either side we need to ensure that the voltage across its. In the early stages of design these models enable accurate estimates of all required powerground grid.

Welcome to our site. IR Drop analysis Static and Dynamic. IR Drop Analysis in Physical Design IR Analysis in VLSI.

The supply voltage of chips is continuously reduced with lower technology node in order to reduce power consumption. The supply voltage decrease and power density increase of future GSI chips demand accurate models for the IR-drop. IR core 775 mV IR package IR pads 5 To determine values for IRpackage and IRpads consider that IRpackage consists of.

Industry Standard Physical Design Live Project. This Drop is called as IR Drop. Abstract A compact IR-drop model for on-chip power distribution networks in wire-bonded ICs is presented.

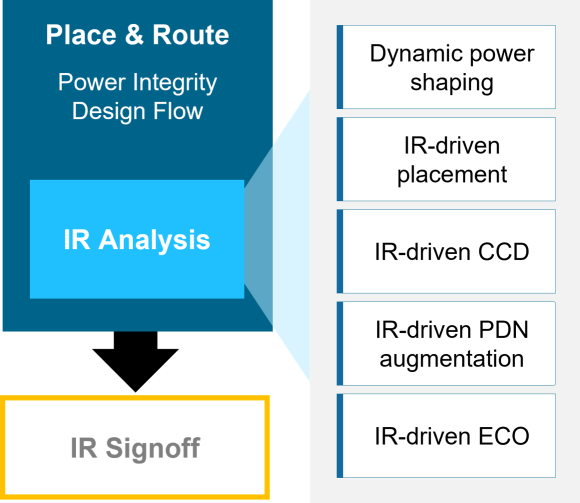

Power requirement of the design Power network structure. As the VLSI industry continues to expand more people are opting for training in the area of the. Just such a solution is available within the Synopsys Fusion Design Platform a RTL-to-GDSII solution enabling a highly convergent full-flow digital implementationSynopsys Fusion Compiler and IC Compiler II provide a production-proven.

Power and Ground nets are usually laid out on the metal layers. The IO pads power and ground buses are built into the pad itself and. When voltage is applied to this metal wires current start flowing through the metal layers and some voltage is dropped due to that resistance of metal wires and current.

Vlsi pnr cts physicaldesign mtech cadence synopsys mentor placement floorplan routing signoff asic lec timing primetime ir electromigratio. VLSI Physical Design Data preparation import design floorplan Power planing power ring core power IO power ring pad bump creattion. Click here to register now.

IR Drop Analysis IR Drop. What is IR drop issue. 5 Real Reasons Why More People Are Increasingly Opting for Physical Design Training.

The voltage that gets to the internal circuitry is less than that applied to the chip since every metal layer offers resistance to the flow of current When a current I passes through a conductor with resistor R it exhibits a voltage drop V which is equal to the resistance times the current. And a whole lot more. This integrated flow provides a complete solution for layout STA IR-drop analysis and optimization and ECOs to fix any issues.

In this create power and ground structure for both IO pads and core logic. In this article we will discuss what is IR drop in ASIC design Why IR drop issue occurs what are the effects of IR drop and how to analyze and prevent the IR drop issue.

Ir Drop Analysis In Physical Design Ir Analysis In Vlsi Team Vlsi

Ir Drop Analysis In Physical Design Ir Analysis In Vlsi Team Vlsi

Overcoming The Growing Challenge Of Dynamic Ir Drop

Ir Analysis Vlsi Back End Adventure

Ir Analysis Vlsi Back End Adventure

Ir Drop Issue In Vlsi What Is Ir Drop In Asic Why Ir Drop Effects Of Ir Drop Youtube

0 comments

Post a Comment